Nanotechnology **18** (2007) 245301 (4pp)

# **Double thermal oxidation scheme for the fabrication of SiO<sub>2</sub> nanochannels**

# Fredrik Persson, L H Thamdrup, M B L Mikkelsen, S E Jaarlgard, P Skafte-Pedersen, H Bruus and A Kristensen<sup>1</sup>

NanoDTU, MIC—Department of Micro and Nanotechnology, Technical University of Denmark, DTU Building 345 East, DK-2800 Kongens Lyngby, Denmark

E-mail: ak@mic.dtu.dk

Received 16 February 2007, in final form 11 April 2007 Published 18 May 2007 Online at stacks.iop.org/Nano/18/245301

#### Abstract

We present a planar fabrication scheme for fluidic systems with silicon dioxide nanochannels and assess the waferscale quality and homogeneity of the fabricated devices. The nanochannels have heights h ranging from 14 to 300 nm and widths w of 2.5, 5 and 10  $\mu$ m. Compared to other state-of-the-art fabrication techniques, our double thermal oxidation scheme (DTOS) displays improvements with respect to 4 inch waferscale height variation  $\sigma_{\rm h} \leq 1.1$  nm and low surface roughness  $R_{\rm a} \leq 0.5$  nm. Our technique is based on well-controlled growth of silicon dioxide, UV lithography, etching, with an etch-stop layer, and glass to silicon dioxide fusion bonding. The smallest achievable channel height is controlled by the precision of oxide growth. The fusion bonding protocol is capable of producing very high aspect ratios, w/h > 2500. We test the devices by measuring capillary filling speed in different channel heights, ranging from 14 to 310 nm. These tests reproduce as well as extend the results reported by Tas et al (2004 Appl. Phys. Lett. 85 3274). A systematic deviation from bulk behaviour has been observed for channel heights below 100 nm.

(Some figures in this article are in colour only in the electronic version)

#### 1. Introduction

This work is motivated by the potential use of nanochannels in the analysis of DNA [1, 2] as well as chemicals [3, 4]. Other uses include fundamental studies of transport phenomena [5] and separation/filtering [6]. Common for these technologies is the need for a simple, reproducible fabrication of nanochannels, as well as fundamental understanding of the liquid and molecular behaviour in nanoconfinements [7]. In the case of DNA an interesting next step would be to stretch single stranded DNA (ssDNA) in nanostructures to gain direct access to the base sequence for gene analysis. Due to the very flexible nature of ssDNA the dimensions have to be scaled down towards a few nanometres [8], which puts tough constraints on the fabrication methods. Techniques for fabricating channels are often divided into the following groups: bulk machining, surface machining, mould machining and bottomup techniques. A comprehensive review of these is given

by Mijatovic et al [9]. Using an etch-stop layer efficiently decreases the problems of etch-rate variations and loading and trenching effects in reactive ion etching (RIE) [10, 11]. A previously reported fabrication method, TMAH etching of silicon, without an etch stop, and a single oxidation step [12], resulted in 4 inch waferscale height variation of  $\sigma_{\rm h} = 2$  nm, while our dry thermal oxide growth can be controlled with a waferscale height uniformity of  $\sigma_h \leqslant 1.1$  nm and a surface roughness of  $R_a < 0.5$  nm, leading to a well determined height for all devices. The small value of  $\sigma_h$  allows for a convenient and reliable comparative analysis of the filling dynamics in devices located at different positions on the wafer and the low  $R_{\rm a}$  allows for the modeling of the fabricated nanochannels as unperturbed structures with a rectangular cross section. The dry thermally grown oxide also has a very high dielectric strength ( $\simeq 10 \text{ GV m}^{-1}$ ) which makes it suitable for handling DNA in narrow channels since the intrinsically negatively charged DNA molecules are often manipulated using electric fields [2].

<sup>&</sup>lt;sup>1</sup> Author to whom any correspondence should be addressed.

Nanotechnology 18 (2007) 245301

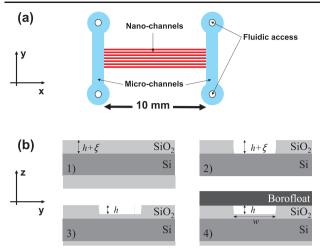

**Figure 1.** (a) Sketch of the design of the fabricated chips. (b) The fundamental steps in the fabrication process: (1) first oxidation; (2) wet isotropic BHF etch forming slightly sloped sidewalls; (3) second oxidation and (4) bonding of lid.

### 2. Fabrication

The fabrication sequence is schematically illustrated in figure 1. The fabrication of the nanochannels consists of four major steps: (1) growth of an initial thermal oxide, (2) UV lithography and isotropic wet etching, (3) growth of the final oxide and (4) bonding.

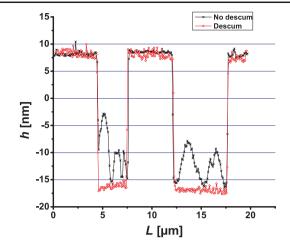

To achieve a final height h of the nanochannels a first dry thermal oxide of height  $h + \xi$  is grown. Subsequently an adhesion layer (HMDS) is applied and 1.5  $\mu$ m thick resist (AZ5214E) is spin-coated. Then the resist is exposed using an Electro Vision (EV) contact UV aligner. After this the exposed resist is developed in an NaOH based developer (AZ351B) followed by an isotropic wet etch using non-oxidizing buffered hydrofluoric acid (BHF, 5 wt%, pH 5) with an etch rate of  $87 \text{ nm min}^{-1}$ . Between the lithographic step and the etching an oxygen plasma descum (time: 10 min,  $O_2$  flow: 50 ml min<sup>-1</sup>,  $N_2$  flow: 50 ml min<sup>-1</sup> and power 150 W) is performed to remove any resist residues causing uneven etching. This step is crucial due to the high selectivity between the photoresist (PR) and SiO<sub>2</sub>. Any residual PR will result in a drastic increase of the surface roughness as shown in figure 2. To obtain fluidic access to the nanochannels another lithographic step, with the same parameters as described previously, is used to define micrometre deep channels connecting the nanochannels to the fluid loading areas, see figure 1. To achieve the required depth, in our case 10  $\mu$ m, the loading areas are defined by etching in the silicon using an advanced silicon etch (ASE) process [13, 22].

At this stage the bottom of the channels is silicon. In order to obtain channels where all surfaces are silicon dioxide, a second oxidation step is performed. Since the growth rate of silicon dioxide decreases with increasing oxide thickness, the secondary oxidation will be faster inside the nanochannel regions than in the surroundings, and the channel height will decrease as the oxide growth progresses. However, the second oxidation will not affect the width of the channels. It is possible to make very accurate predictions of the two-step F Persson et al

**Figure 2.** Profilometer line scans across two consecutive 25 nm deep channels, one for a wafer which has gone through a descum before the etching and one that has not had the descum treatment. The sample where the descum treatment was omitted displays a very rough channel floor with protrusions of heights between 5 and 10 nm, up to 40% of the channel height. The two wafers were processed in parallel, so that the development and etching was performed identically for both wafers.

oxidation process using the analytical Deal–Grove model [14] or revised versions thereof [15]. Especially when dealing with oxide thicknesses below 30 nm the revised versions of the Deal–Grove model must be applied in analytical calculations. Another approach is utilizing commercial simulation programs such as SSUPREM [16], which has been used with satisfactory results.

Liquid access holes are sandblasted through the Pyrex lid wafer, using a microetching tool [17]. To protect the surface that is to be bonded, a 4.2  $\mu$ m layer of photoresist (AZ5214E) is spin-coated. Subsequently both sides of the wafer are covered with Nitto SWT 70  $\mu$ m thick blue film which acts like a mask for the sand blasting. The holes are marked in the film on both sides using a 150 W CO<sub>2</sub> laser running at 5% power with a scan speed of 200 mm s<sup>-1</sup>. The sandblasting particles are Al<sub>2</sub>O<sub>3</sub> particles of diameter 50 or 110  $\mu$ m. The holes are blasted from the backside, i.e. the non-bonding side, to keep the bonding surface as unperturbed as possible. The holes used are typically around 100  $\mu$ m in diameter.

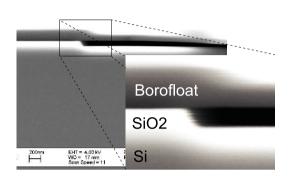

The Borofloat (Pyrex) glass lid and the silicon substrate wafers were bonded by a fusion bonding process which was chosen to avoid sagging of the lid into the shallow channels. A chemical treatment using  $H_2SO_4$ : $H_2O_2 = 4:1$  for 15 min, rinsing in DI water for 5 min and 25 wt% NH<sub>4</sub>OH for 40 min was used to activate the bonding surfaces through the formation of hydroxyl groups. After the chemical treatment the wafers were rinsed in DI water and spin-dried. A prebond, where the two wafers are held together by van der Waals forces, was obtained by pressing the wafers together by hand. To achieve the final covalent bond an annealing step by heating the prebonded wafers to a peak temperature of 550 °C at 120 °C h<sup>-1</sup>, leaving them for 5 h and then cooling them to room temperature at 250 °C h<sup>-1</sup>. The final result is shown in figure 3.

The channel heights above 50 nm were measured by a surface profiler (Dektak 8), while the shallower channels were

**Table 1.** Table documenting the high degree of 4 inch waferscale height uniformity of the fabricated nanochannels.  $h_{av}$  is the average height and  $\sigma_h$  is the variation. Measurements were performed by using either a Dektak 8 stylus profiler with a tip radius of 5  $\mu$ m (marked with an asterisk) or tapping mode AFM. When using the stylus profiler measurements were carried out at four places on the wafer periphery and in the centre, whereas the AFM measurements were carried out at two places on the periphery and in the centre. Two wafers where the initial oxide was grown using a wet thermal oxidation have been included for comparison.

|                 | Dry oxidation |      |      |      |       |        |        | Wet oxidation |        |

|-----------------|---------------|------|------|------|-------|--------|--------|---------------|--------|

| $h_{\rm av}$    | 14.6          | 22.3 | 33.0 | 49.3 | 78.4* | 104.0* | 158.1* | 195.6*        | 269.3* |

| $\sigma_{ m h}$ | 0.3           | 0.2  | 0.6  | 0.4  | 0.7   | 0.8    | 1.1    | 4.4           | 6.2    |

**Figure 3.** SEM micrograph showing the cross section of a fusion bonded nanochannel with height h = 75 nm and width  $w = 10 \ \mu$ m.

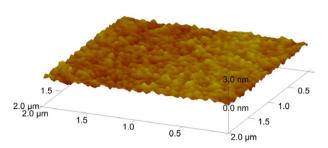

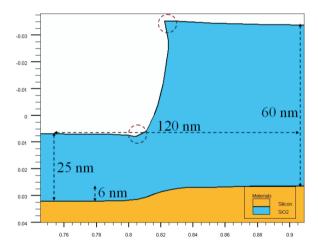

measured by AFM in tapping mode. In order to document the 4 inch waferscale height uniformity, the average height and standard deviation for nine different wafers are presented in table 1. In the case of nanochannels fabricated solely using dry thermal oxidations the random uncertainty (i.e.  $U_{\rm h}$  =  $\sigma_{\rm h}/\sqrt{N}$ , where N is the number of independent measurements) on the height measurements is below 1 nm. This does not, of course, include any systematic uncertainties, which could bias the height measurements, but it indicates that the double thermal oxidation scheme provides a platform for fabricating structures with state-of-the-art height uniformity. Even when utilizing a wet thermal oxidation for the initial oxide the random uncertainty is of the order of 2.5 nm. The surface roughness measurements were carried out using an AFM in tapping mode. A scan displaying the low surface roughness is shown in figure 4. Investigations with SEM and dark field optical microscopy, following the procedures of [18], revealed that our fusion bonding protocol is capable of achieving aspect ratios as high as w/h > 2500 without any signs of collapse or sagging. This is a factor of 5 higher than recently reported results [18, 19]. Studies indicated that the channels exhibit a small apex and void being formed during the second oxidation since O<sub>2</sub> reacts with the Si substrate at the bottom and by diffusing through the first oxide, constituting the wall, and reacting, which was also predicted by simulations, see figure 5. For a given height of the initial oxide this effect can be decreased by growing a thinner final oxide layer, although we have not observed any difference in bonding quality comparing with devices fabricated without the second oxidation step. The sloped sidewalls caused by the isotropic wet etch step, see figure 3, can be avoided by using a dry reactive ion etching process instead, which also makes it possible to achieve welldefined two-dimensional nanochannels.

**Figure 4.** AFM (tapping mode, 1.45  $\mu$ m s<sup>-1</sup>) scan in the bottom of a channel showing the low surface roughness. In this scan the roughness is measured to  $R_a = 0.241$  nm.

**Figure 5.** Picture showing the result of a SSUPREM4 simulation of the double oxidation. The first dry oxidation was performed at  $1050 \,^{\circ}$ C for 32 min resulting in 50 nm SiO<sub>2</sub>. After UV lithography a 52 s BHF etch was simulated followed by the final dry oxidation at  $1000 \,^{\circ}$ C for 20 min resulting in a 25 and 60 nm thick oxide at the nanoslit bottom and sidewall, respectively. Notice the slightly concave and convex shape of the oxide to the right and left of the nanoslit wall, respectively. The small apex and void (marked by dashed circles) result in a height difference of about 2 nm as compared to the baseline of the oxide to the right and left, respectively.

## 3. Capillary filling experiments

The devices were tested by measuring capillary filling speed in different channel heights, where we reproduce and extend the results in [20]. Our measurements by optical microscope and video camera of capillary filling speeds include 5 and 10  $\mu$ m wide channels with heights ranging from 14 to 310 nm, thus extending the previously reported height range. The position L(t) as a function of time t of the front meniscus during capillary filling depends on surface tension,  $\gamma$ , viscosity

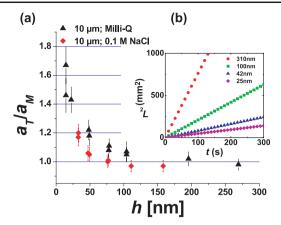

**Figure 6.** (a) The ratio  $a_T/a_M$  of the theoretically calculated slope  $a_T$  and the measured slope  $a_M$  plotted versus channel height *h*. The filling liquids are Milli-Q water and an 0.1 M NaCl aqueous solution. Every data point is an averaged value from between 20 and 50 measurements. Note that the uncertainties presented take into account the uncertainty in the theoretical value and the spread in the measured values are much smaller. The channel width presented is 10  $\mu$ m but identical results have also been obtained for channels with a width of 5  $\mu$ m. (b) The plot shows the linear relationship between  $L^2(t)$  and *t* for heights between 25 nm and 310 nm. There is a very high correlation for this relation,  $R^2 > 0.999$ , in all data points presented in (a).

$\eta$  and the advancing contact angle  $\theta$ . As expected from the Washburn model [21], the square of the position increases linearly in time as shown in figure 6. Modifying the model to take into account the rectangular cross sections of the channels yields the following relation:

$$L(t)^{2} = a_{T} t \qquad \text{where } a_{T} = \frac{\gamma \cos \theta}{3\eta} h \left( 1 - 0.63 \frac{h}{w} \right).$$

(1)

However, as seen in figure 6, for heights *h* below 100 nm the measured slopes  $a_{\rm M}$  grows systematically larger than the theoretically expected slope  $a_{\rm T}$ . In [20] this deviation is attributed to the electro-viscous effect. We also observe a corresponding deviation for 0.1 M NaCl (aq) solution appearing at channel heights below 50 nm, see figure 6. In light of this, and considering that the NaCl solution has a Debye length of  $\lambda_{\rm D} \approx 1.0$  nm, we conclude that other effects, besides the electro-viscous effect, contribute to the observed deviations.

#### 4. Conclusion

A simple and well-controlled fabrication technique yielding low 4 inch waferscale height variation, surface roughness and high possible aspect ratios has been achieved. In the subsequent measurements of capillary filling, we have identified a threshold height of about 100 nm, below which deviations from bulk fluidics are significant and systematic.

In the future we plan to further develop this fabrication scheme to achieve two-dimensional nanochannels by combining it with an advanced oxide etch (AOE) process [13].

#### Acknowledgment

This work was supported by the Danish Research Council for Technology and Production (FTP), grant no. 274-050375.

### References

- Reisner W, Morton K, Riehn R, Wang Y, Yu Z, Rosen M, Sturm J, Chou S, Frey E and Austin R 2005 *Phys. Rev. Lett.* 94 196101

- [2] Fu J, Yoo J and Han J 2006 Phys. Rev. Lett. 97 018103

- [3] Stern M, Geis M and Curtin J 1997 J. Vac. Sci. Technol. B 15 2887–91

- [4] Kameoka J and Craighead H 2001 Sensors Actuators B 77 632–7

- [5] Stein D, Kruithof M and Dekker C 2004 Phys. Rev. Lett. 93 035901

- [6] Wang Y C, Fu J, Mao P and Han J 2005 TRANSDUCERS '05: The 13th Int. Conf. on Solid-state Sens. Act: Microsyst. Digest of Technical Papers pp 352–5

- [7] Bakajin O, Duke T, Chou C, Chan S, Austin R and Cox E 1998 *Phys. Rev. Lett.* 80 2737–40

- [8] Dessinges M N, Maier B, Zhang Y, Peliti M, Bensimon D and Croquette V 2002 Phys. Rev. Lett. 89 248102

- [9] Mijatovic D, Eijkel J and van den Berg A 2005 Lab Chip 5 492–500

- [10] Hedlund C, Blom H O and Berg S 1994 J. Vac. Sci. Technol. A 12 1962–5

- [11] Hwang S W, Lee G R, Min J H and Moon S 2004 J. Vac. Sci. Technol. B 22 1953–7

- [12] Haneveld J, Jansen H, Berenschot E, Tas N and Elwenspoek M 2003 J. Micromech. Microeng. 13 S62–6

- [13] Trademark of Surface Technology Systems Limited (STS), UK www.stsystems.com

- [14] Deal B and Grove A 1965 J. Appl. Phys. 36 3770-8

- [15] Kim K, Lee Y, An M, Suh M, Youn C, Lee K and Lee H 1996 Semicond. Sci. Technol. 11 1059–64

- [16] Part of ATHENA simulation package, Silvaco International www.silvaco.com

- [17] Microetcher II, Danville Engineering www.daneng.com

- [18] Mao P and Han J 2005 *Lab Chip* **5** 837–44

- [19] Liao K P, Yao N K and Kuo T S 2006 Proc. 28th IEEE EMBS Annual Int. Conf. pp 2832–5

- [20] Tas N, Haneveld J, Jansen H, Elwenspoek M and van den Berg A 2004 Appl. Phys. Lett. 85 3274–6

- [21] Washburn E 1921 Phys. Rev. Lett. 17 273-83

- [22] Laermer F and Schilp A 1996 Method of Anisotropically Etching Silicon German Patent DE4241045C1, US Patent 4855017 and 4784720